离子束刻蚀机厂家分享接触孔的等离子体蚀刻

离子束刻蚀机厂家分享接触孔的等离子体蚀刻:

接触孔在集成电路的制造中起到承上启下、连接前段器件和后段金属互连的重要作用。由于接触孔层在集成电路中起到的关键作用,在接触孔蚀刻工艺中,工艺整合对于接触孔关键尺す、尺す均匀性、接触孔侧壁形状的控制,以及接触孔蚀刻工艺对蚀刻停止层的选择性、金属硅化物的消耗量、接触孔高度均匀性及确保接触孔全部开通的要求越来越严格,特别是对于良率的提高变得越来越重要。

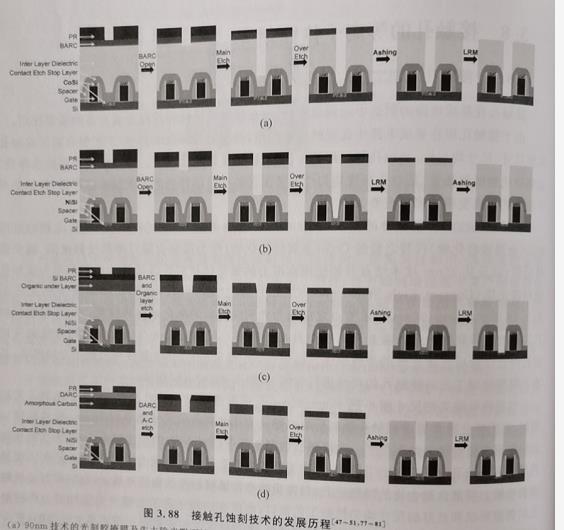

在接触孔技术工艺整合的发展历程中,两个重要的里程碑是65mm技术结点开始使用NiSi(金属镍硅化物)代替之前的CoS(金属钻硅化物)作为接触金属以降低接触电阻、减少信号延迟,以及从45nm技术结点开始使用高应力的氮化硅材料改善器件的性能并作为接触孔蚀刻停止层( Contact Etch Stop Layer,CESL)。与之相伴随的接触孔蚀刻技术的发展如图3.88所示,65nm/55nm技术节点之前均为光刻胶掩膜的氧化硅材料蚀刻,90nm时的接触孔蚀刻的步骤顺序为先去除光阻再蚀刻开接触孔停止层,而65mm/55nm时使用先蚀刻开接触孔停止层后去除光阻的步骤顺序。由于90nm和65nm/55nm器件对关键尺寸的要求,基本不需要蚀刻工艺对接触孔的尺す进行收缩,如图3.88(a)、(b)所示。

当逻辑电路关键尺寸缩小到45nm/40nm及更先进的工艺技术节点时,由于光刻工艺的限制,工艺整合通常要求接触孔蚀刻后的关键尺す比蚀刻前的尺す缩小约40nm(尺す偏移)开始使用多层掩膜的蚀刻技术。在接触孔蚀刻工艺中,如此巨大的尺す缩小,对确保接触孔在高深宽比情形下的开通提出了挑战,尺寸偏移通常主要通过富含聚合物的蚀刻工艺来实现尺寸的收缩。而富含聚合物的蚀刻工艺,趋向于减小保证接触孔的良好开通、控制高深宽比接触孔的侧壁形状和良好的尺寸均匀性的工艺窗口,而所有这些正是工艺整合为实现更为严格的电性特征提出的对蚀刻工艺的要求。除此之外,光刻技术对于图形曝光需要厚度更薄的、更少未显影的光刻胶,这些要求又增加了接触孔蚀刻工艺对光刻胶的更高的选择性,来防止接触孔的圆整度变差。因此,为更好的传递图形,45nm/40nm开始使用有机旋涂的多层掩膜技术(从下至上依次是有机旋涂层( Organic under Layer)、有机材料抗反射层( Si BARC)和光刻胶);发展到28nm技术时,开始使用先进图形材料的多层掩膜技术(从下至上依次是先进图形材料层( Amorphous Carbon)、硬掩膜抗反射层(DARC)和光刻胶)。其中,有机旋涂多层掩膜技术使用的旋涂层为碳氢聚合物,有机材料抗反射层为含硅的碳氢聚合物,二者都是液体,需经过低温烘烤成固态掩膜,因此称为软掩膜技术,都是在光刻机台上一体化完成,具有很快的工艺过程。而先进图形材料的多层掩膜是化学气相沉积的先进图形材料(无定型碳薄膜)以及介电材料(如氮氧化硅)薄膜作为抗反射层,因此又称为硬掩膜技术。由于硬掩膜技术中使用的氯氧化硅材料的厚度很薄,大概是软掩膜技术中的有机材料抗反射层的厚度的1/2或1/3,因此,为传递图形所需要的光刻胶的厚度也可以大大降低,这样可以显著增加光刻工艺的图形显影精准度、降低噪声影响及提高安全工艺窗口;同时,先进图形材料掩膜层工艺还具有更高的接触孔尺寸收缩能力及更优异的接触孔圆整度,由此可见,图3.88(d)的先进图形材料多层掩膜技术能更好地传递图形,具有优良的工艺整合的工艺窗口,被广泛使用于目前前沿的逻辑集成电路制造工艺流程中

感谢大家耐心看完,如果需要了解更多关于离子束刻蚀机的相关知识,欢迎联系我们!

下一条: 离子束刻蚀机厂家分享先进侧墙蚀刻技术